## Designs of Fully On-chip Antennas in (Bi)CMOS Technology

### Shiji Pan, Leland Gilreath, Payam Heydari, and Filippo Capolino

Department of Electrical Engineering and Computer Science, University of California-Irvine 4131 Engineering Hall, University of California-Irvine, Irvine, CA, USA 92697 Email:shijip@uci.edu, f.capolino@uci.edu

**ABSTRACT:** The paper presents several feasible millimeter wave on-chip antenna designs suitable to be fabricated in CMOS technology without any additional process. The results are listed and compared with state-of-the-art designs in the literature. The difficulties in designing high efficiency antenna on CMOS chip are discussed.

#### INTRODUCTION

CMOS technology has been proven as an effective platform for low power millimeter wave (mmWave) transceiver systems. For near-future applications of mmWave receivers with on-chip antennas (OCAs), such as mmWave imaging and multi-gigabit-per-second short range wireless communications, it is strongly desirable to achieve high efficiency antennas, which would lead to integrated systems with efficiency much higher than the current state of the art. In terms of bandwidth, a wideband antenna performance is also required. Besides, for the purpose of cost, a miniaturized size is also a prerequisite for on-chip antenna.

However, it is very challenging to achieve a high gain, wide band and high efficiency on-chip antenna by CMOS technology. Antenna radiating above a lossy silicon substrate usually results in very low radiation efficiency. Another concern is the electromagnetic interference (EMI) phenomenon when antenna and front-end are in proximity range and sharing the same substrate [1]. To alleviate these problems, a ground plane at lower metal layer inside CMOS (e.g., M1, the lowest metal layer) is preferable to stop the wave travelling inside the lossy silicon and hereby suppress the EMI. However, since the extremely thin total thickness of silicon dioxide (typically around 1% guided wavelength in silicon dioxide), a ground plane at M1 strongly limits the antenna substrate thickness and therefore limits the bandwidth, and meanwhile ohmic losses get much stronger so that the antenna radiation efficiency gets strongly degraded.

In this review paper, several proposed on-chip antenna designs are shown and the results are organized in Table 1 to compare some of our work to the state-of-the-art CMOS on-chip antennas in the literature. Based on the results, it can be observed that on-chip antenna design without extra process, with a ground plane below silicon and a ground plane at M1 (inside silicon dioxide) will provide more and less similar gain level and the latter case implies a narrower bandwidth. The designs of lens-based antenna [2, 3], superstrate antenna [4], and through-substrate-via (TSV) based antenna [5] show high gain but require extra process and/or exhibit bulky sizes. In [6, 7], the potential to use high impedance surface (HIS) or artificial magnetic conductor (AMC) for OCA application was explored. In [6, 8], it was reported that in addition to placing HIS below a dipole antenna to act as a reflection layer, HIS could also be excited as a radiator directly by means of the leaky mode property inside the structure.

# PROPOSED CMOS ON-CHIP ANTENNA

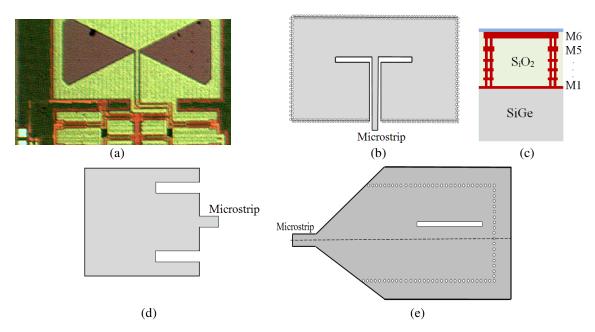

Several high performance on-chip antennas have been investigated at the authors' institution, shown in [6, 9, 10]. Their configurations are shown in Fig.1 and Fig.2 and their main results are summarized and organized in Table.1. Fig.1 (a) shows the micrograph of a bowtie slot antenna fabricated in 180 nm BiCMOS process. The bowtie slot antenna is placed at top metal layer (M6) and with a ground plane below silicon substrate. The measured results of the bowtie antenna show a very wide bandwidth, covering the most of the W-band (from 70 GHz to 110 GHz).

Fig.1 (b) and (c) show the top view and side view of a cavity backed slot antenna fed by a microstrip line. The cavity is composed by top and bottom metal layer (M6 and M1) and vias in between. The cavity functions not only as a shielding structure to prevent the overwhelming dielectric loss in silicon but also enhance the slot antenna radiation. The slot antenna is fed by the microstrip line directly and also by the  $TE_{110}$  cavity mode. It was concluded that when properly choosing the location of the slot, the two feeding mechanism would be constructive and improve the antenna gain.

Fig.1 (d) shows the top view of an extremely flat E-shape patch antenna. The patch antenna is located at M6 and has a ground plane at M1. The bandwidth of the patch antenna is enhanced by creating an additional resonance due to the two notches. Despite the extremely thin antenna substrate (9.6 μm), a 13 GHz bandwidth has been achieved for a 94 GHz E-shape patch design. Also, among W-band antennas listed in Table.1, the E-shape patch antenna has the smallest area usage, which is abstracting in terms of cost. Fig.1 (e) shows a slot antenna over an extremely thin substrate integrated waveguide. The waveguide is realized between M1 and M6, and vias in between, which is similar to the cavity in Fig.1 (c). A taping shape microstrip is used to match the 50 ohm microstrip line with the waveguide.

Fig. 1 (a) Micrograph of bowtie antenna; (b) top view of extremely flat (9.6 µm) cavity backed slot antenna; (c) side view of the extremely flat cavity backed slot antenna; (d) top view of the extremely flat E-shape patch antenna; (e) top view of an extremely flat substrate integrated waveguide antenna. Designs (b)-(e) are extremely flat because they have a ground plan at M1.

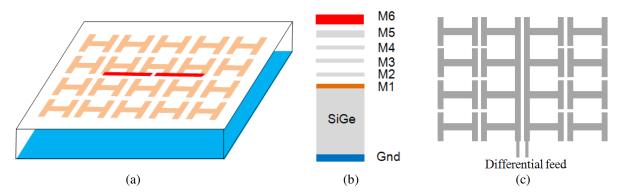

The configuration of using HIS in CMOS OCA design is shown in Fig.2. Fig.2 (a) shows the design of HIS below a dipole antenna, by patterning M1. The ground of the HIS is placed below the Si-Ge layer. The HIS is acting as an artificial magnetic conductor (AMC) at the designed frequency band. In [6], it was also reported that HIS could be fed directly as radiator without dipole on the top. The HIS is located at top metal layer M6, with a ground plane at M1. As explained in [8], a TM-like leaky mode is excited inside the HIS with a large attenuation constant, which is due to the strong ohmic losses. And because of the large attenuation constant, only a small numbers of periodic elements are employed in the antenna design, which is different from traditional large number of elements in highly directive leaky wave antennas.

Fig. 2 (a) Dipole antenna above HIS (b) side view of dipole over HIS (c) top view of HIS antenna without dipole

The performance of all the antennas mentioned above and state-of-the-art OCAs is listed in Table 1, including the antenna size, operating frequency, bandwidth and peak gain. According to Table 1, off-chip antennas (i.e., antennas that requires extra process off-chip), especially antennas with lens, exhibit much higher gain. Novel designs should be investigated to improve the gain and gain bandwidth of on-chip antennas and achieve a wider bandwidth for on-chip antennas with extra process.

Tab. 1 Performance of proposed (Bi)CMOS on-chip antennas and other state-of-the-art work

| Our work                          |       |                    |                   |                |         |                |

|-----------------------------------|-------|--------------------|-------------------|----------------|---------|----------------|

|                                   | Freq. | Chip area          | Gain (dBi)        | -10dB          | Fully   | Isolation with |

|                                   | (GHz) | $(mm \times mm)$   |                   | input BW (GHz) | on-chip | circuits       |

| Bowtie slot [9]                   | 94    | $1.4 \times 0.9$   | 1 (mea.)          | 40 (mea.)      | Yes     | No             |

| Cavity backed slot [10]           | 140   | $1.2 \times 0.6$   | -2 (sim.)         | 7 (sim.)       | Yes     | Yes            |

| E shape patch [9]                 | 140   | $0.7 \times 0.7$   | -2 (sim.)         | 10 (sim.)      | Yes     | Yes            |

| E shape patch                     | 94    | $1.2 \times 0.8$   | -3 (sim.)         | 13 (sim.)      | Yes     | Yes            |

| HIS antenna with dipole [6]       | 94    | $2.2 \times 1.2$   | 1 (sim.)          | 12 (sim.)      | Yes     | No             |

| HIS antenna w/o dipole [6]        | 140   | $1.4 \times 0.9$   | - 1.5 (sim.)      | 12 (sim.)      | Yes     | Yes            |

| Waveguide slot [9]                | 140   | 2 × 0.6            | 0 (sim.)          | 5 (sim.)       | Yes     | Yes            |

| Examples of state-of-the-art work |       |                    |                   |                |         |                |

| Patch fed by TSV [5]              | 110   | N/A                | -3 (mea.)         | 10 (mea.)      | Yes     | No             |

| Patch with ground at M4 [11]      | 60    | $1.22 \times 1.58$ | -3.23 (mea.)      | 0.81(mea.)     | Yes     | Yes            |

| Slot with lens [2]                | 90    | $1.8 \times 1.4$   | - 5.7 (mea.)      | 4 GHz          | No      | Yes            |

|                                   |       |                    | w/o lens          |                |         |                |

|                                   |       |                    | 15 (sim.) w/ lens |                |         |                |

| Dipole with lens [3]              | 60    | NA                 | 8 (mea.)          | NA             | No      | No             |

| Patch with superstrate [4]        | 94    | 1.6 × 1            | 3 (mea.)          | 6 (mea.)       | No      | Yes            |

## ON-CHIP ANTENNA RADIATION MEASUREMENT

Measurement of on-chip antenna gain and radiation pattern is challenging due to several constraints. One of the difficulties is that the antenna feed probe has to be in the very proximity near-field range of the OCA. For off-chip antenna (e.g., antenna in package), this issue could be avoided by feeding the antenna in the backside of the antenna main beam. Figure 3 shows our setup for the antenna gain measurement. For the figure visibility, the absorbers are removed in the range around the probe station. A signal generator drives a ×6 frequency multiplier, providing the W-band power to a transmit W-band horn antenna.

Fig. 3 On-chip antenna measurement setup. Signal is transmitted by a horn antenna on a rotating arm. The onchip bowtie slot antenna is probed and the received signal is down-converted, and then measured with a spectrum analyzer.

At the receiving side, a harmonic mixer is employed to down-convert the frequency and connects to spectrum analyzer. A rotary table and rotation arm enables the pattern measurement. The antenna gain calibration is based on two W-band horn antennas separated at the same distance between horn antenna and the on-chip antenna. Losses in the probes and additional 0.5 dB transition loss between probe and on-chip coplanar waveguide were considered in the gain calculation of the bow tie antenna. However, due to strong interferences, the measured (averaged) 1dB gain is to be considered an approximate value.

#### REFERENCES

- [1] Y. P. Zhang and D. X. Liu, "Antenna-on-Chip and Antenna-in-Package Solutions to Highly Integrated Millimeter-Wave Devices for Wireless Communications," *IEEE Transactions on Antennas and Propagation*, vol. 57, pp. 2830-2841, Oct 2009.

- [2] J. M. Edwards and G. M. Rebeiz, "High-efficiency silicon RFIC millimeter-wave elliptical slot-antenna with a quartz lens," in Antennas and Propagation (APSURSI), 2011 IEEE International Symposium on, 2011, pp. 899-902.

- [3] A. Babakhani, D. B. Rutledge, and A. Hajimiri, "mm-wave phased arrays in silicon with integrated antennas," in Antennas and Propagation Society International Symposium, 2007 IEEE, 2007, pp. 4369-4372.

- [4] J. W. May, R. A. Alhalabi, and G. M. Rebeiz, "A 3 G-Bit/s W-Band SiGe ASK Receiver with a High-Efficiency On-Chip Electromagnetically-Coupled Antenna," in 2010 IEEE Radio Frequency Integrated Circuits Symposium (RFIC 2010), Anaheim, CA., 2010, pp. 87-90.

- [5] H. Sanming, W. Lei, X. Yong-Zhong, L. Teck Guan, Z. Bo, S. Jinglin, and Y. Xiaojun, "TSV Technology for Millimeter-Wave and Terahertz Design and Applications," *Components, Packaging and Manufacturing Technology, IEEE Transactions on*, vol. 1, pp. 260-267, 2011.

- [6] S. Pan, D. Wang, C. Guclu, and F. Capolino, "High impedance layer for CMOS on-chip antenna at millimeter waves," in Antennas and Propagation (APSURSI), 2011 IEEE International Symposium on, 2011, pp. 903-906.

- [7] L. Fujiang and O. Ban Leong, "Integrated millimeter-wave on-chip antenna design employing artificial magnetic conductor," in 2009 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT 2009), Singapore, Singapore, 2009, pp. 174-177.

- [8] C. Guclu, J. Sloan, S. Pan, and F. Capolino, "Direct Use of the High Impedance Surface as an Antenna Without Dipole on Top," *Antennas and Wireless Propagation Letters*, *IEEE* (in press).

- [9] S. Pan, D. Wang, and F. Capolino, "Novel high efficiency CMOS on-chip antenna structures at millimeter waves," in Antennas and Propagation (APSURSI), 2011 IEEE International Symposium on, 2011, pp. 907-910.

- [10] S. Pan and F. Capolino, "Design of a CMOS On-Chip Slot Antenna With Extremely Flat Cavity at 140 GHz," Antennas and Wireless Propagation Letters, IEEE, vol. 10, pp. 827-830, 2011.

- [11] H. Kuo-Ken and D. D. Wentzloff, "60 GHz on-chip patch antenna integrated in a 0.13-μm CMOS technology," in Ultra-Wideband (ICUWB), 2010 IEEE International Conference on, 2010, pp. 1-4.